電路板與集成電路設(shè)計(jì) 技術(shù)演進(jìn)與應(yīng)用前景

電路板和集成電路設(shè)計(jì)是現(xiàn)代電子技術(shù)的核心,它們共同推動(dòng)了從智能手機(jī)到超級(jí)計(jì)算機(jī)的眾多創(chuàng)新。電路板作為電子元件的物理載體,而集成電路則將復(fù)雜的電路系統(tǒng)微縮到單個(gè)芯片上,二者協(xié)同工作,構(gòu)成了電子設(shè)備的基礎(chǔ)。

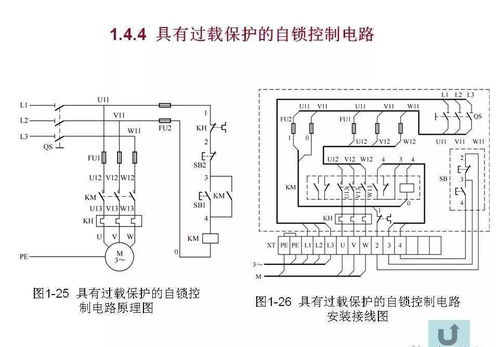

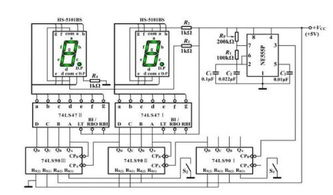

在電路板設(shè)計(jì)中,工程師需要考慮布局、布線、信號(hào)完整性和熱管理等因素。隨著高頻和高速應(yīng)用的發(fā)展,多層板和柔性電路板的應(yīng)用日益廣泛。例如,在5G通信設(shè)備中,電路板必須處理高頻信號(hào)并減少電磁干擾,這要求精密的阻抗控制和屏蔽設(shè)計(jì)。

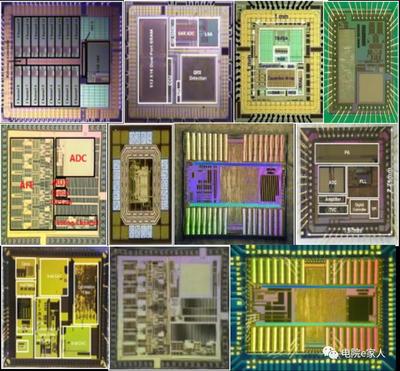

集成電路設(shè)計(jì)則更加微觀,涉及晶體管級(jí)的設(shè)計(jì)與優(yōu)化。現(xiàn)代IC設(shè)計(jì)流程包括邏輯設(shè)計(jì)、物理設(shè)計(jì)、驗(yàn)證和測(cè)試等階段。以系統(tǒng)級(jí)芯片(SoC)為例,工程師將處理器、內(nèi)存和外圍接口集成在一個(gè)芯片上,實(shí)現(xiàn)了高性能與低功耗的平衡。人工智能和物聯(lián)網(wǎng)的興起進(jìn)一步推動(dòng)了專用集成電路(ASIC)和現(xiàn)場(chǎng)可編程門陣列(FPGA)的發(fā)展,使得定制化芯片設(shè)計(jì)成為可能。

盡管電路板和集成電路設(shè)計(jì)各有側(cè)重,但它們密切相關(guān)。電路板為IC提供電源和信號(hào)連接,而IC的性能又影響電路板的布局要求。未來,隨著三維集成和異質(zhì)集成技術(shù)的進(jìn)步,電路板與芯片的界限可能進(jìn)一步模糊,例如通過硅通孔(TSV)技術(shù)實(shí)現(xiàn)堆疊芯片設(shè)計(jì)。

電路板和集成電路設(shè)計(jì)是電子行業(yè)的兩大支柱,它們的持續(xù)創(chuàng)新將驅(qū)動(dòng)下一代智能設(shè)備、自動(dòng)駕駛和綠色能源等領(lǐng)域的突破。工程師必須掌握跨學(xué)科知識(shí),以應(yīng)對(duì)日益復(fù)雜的設(shè)計(jì)挑戰(zhàn)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.musi365.com/product/5.html

更新時(shí)間:2026-01-13 02:19:34